## Medium Voltage Solid State Transformer for Grid Applications; Opportunities and Challenges

© 2023 Eaton Research Labs. All rights reserved

**Dr. Bogdan Borowy**

**Senior Chief Engineer**

**Eaton Research Labs**

- SST Topology Selection

- MV SST Topology

- Design Challenges

- MV SST Applications

- Utility Requirements

- Outlook

## Solid State Transformer Topology

- Needs

- High Power Applications

- Distribution Voltage Level MV (> 4.16 kV)

- Bidirectional Power Flow

- Enhanced controls (power, voltage, distribution)

- Renewables adaptable

- High Power Quality

- Active Filtering

- Agile and Stabilizing

- Power Router

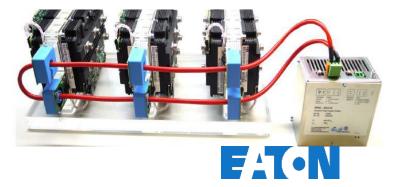

50Hz 10kHz Freq. 2MW/unit 56kW/unit Power Quantity lpcs 36pcs Power 0.77kW/L 14kW/L density 2MW 6000kg 666kg weight

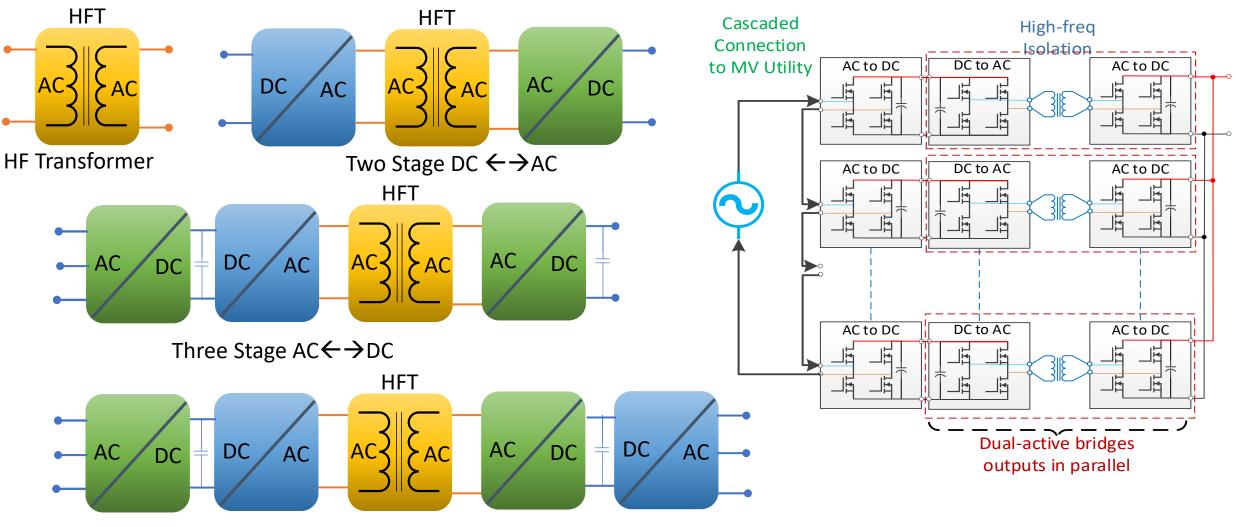

- Topologies Derivation

- Operating Voltage → Multilevel OR Multiple

Devices in Series

- High Control Bandwidth → High Switching

Frequency

- Flexible Power Router  $\rightarrow$  DC Bus Distribution

- Isolation (safety)  $\rightarrow$  Transformer

- Small Volume / Footprint / Weight → HF

Magnetics

#### Solid State Transformer Topology Selection

Four Stage  $AC \leftrightarrow AC$

#### Topology Selected MV SST and Design Challenges

FAT•N

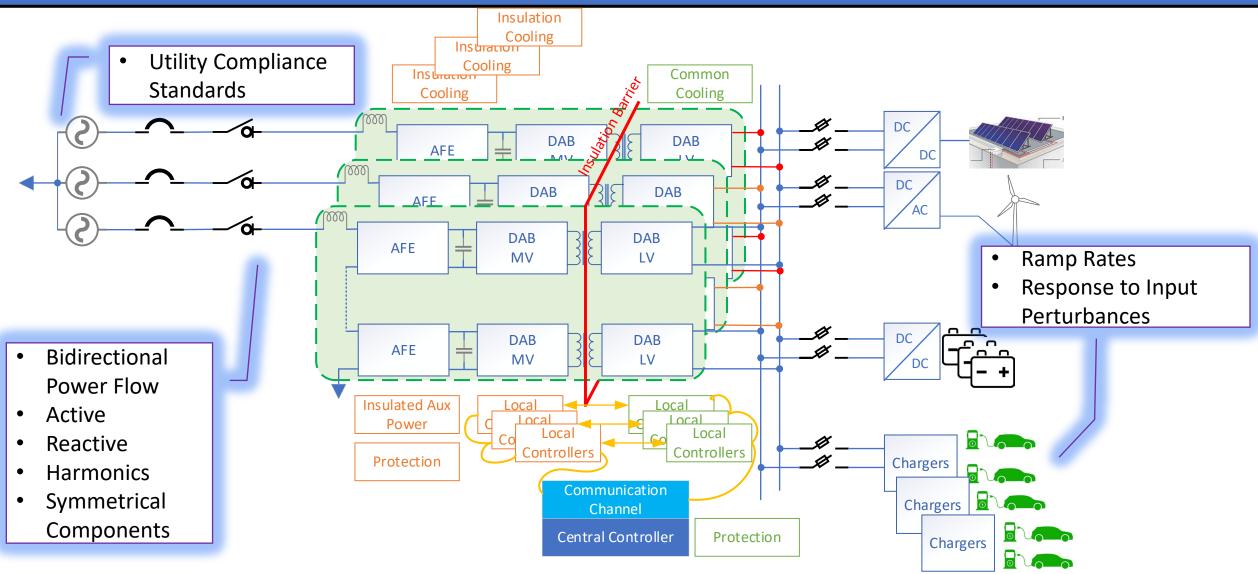

## **MV SST Design Challenges**

- Low Short Circuit Capability

- Isolation

- 95 kV BIL for 15 kV Class

- Transformer Fabrication

- Isolation Power Supply for Hotel Power

- Cooling Loop Conductivity

- EMI and Common Mode Voltages

- Complex Controls & Communications

- AFE: MV DC Bus Voltage Balancing

- DAB: Power / Current Balancing

- Central Controller serving all levels communication protocol

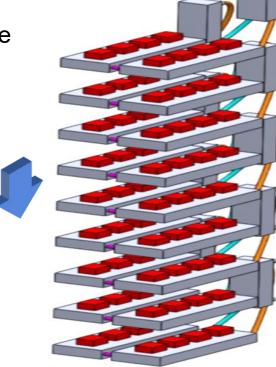

- HF Transformer

- HV Insulation

- Partial Discharge

- LV←→MV BIL of 95 kV required

- Parasitic Capacitances  $\rightarrow$  Stray Losses, EMI

- Core and Windings Insulation

- Core Cooling often required (HF  $\leftarrow \rightarrow$  size)

- Thermal

- Individual Cooling Loops for each level

- Advanced Materials Use

- Phase-change

- Immersive Cooling

- Switching Devices

- Soft-Switching at all power levels

© 2023 Eaton Research Labs. Mrgh DC Bus Capacitance optimization

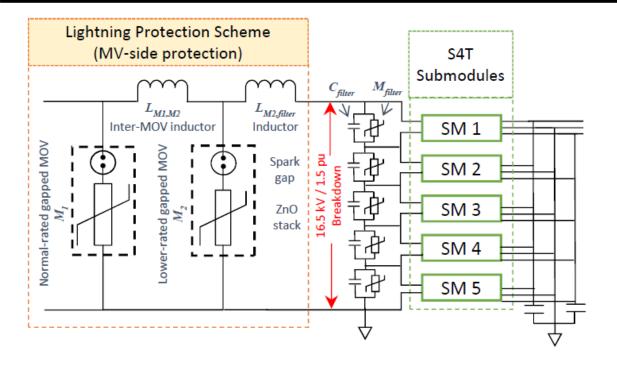

## Selected MV SST Design Challenge Mitigations

- Front End (MV) Protection

- 15 kV Class → BIL 95 kV

- Isolated Power Supplies

- Gate Drivers

- Local Controllers Supply

#### Selected MV SST Design Challenges Mitigations (cont.)

- Cooling

- MV Conversion Stage Electrically "Floating"

- Cold-plates in series/parallel: De-Ionized Water (reliability and maintenance concerns)

- Individual Cold-plate Loops (modular, integrated with Level converters, require secondary loop)

- Advanced Cooling (materials, coolant types, pumpless)

- Thermosyphon

- Immersive Cooling

- HF Transformer

- Shielding

# HF Transformer Characterization: MV SST Parasitics

Fig. 6 Common Mode Capacitance

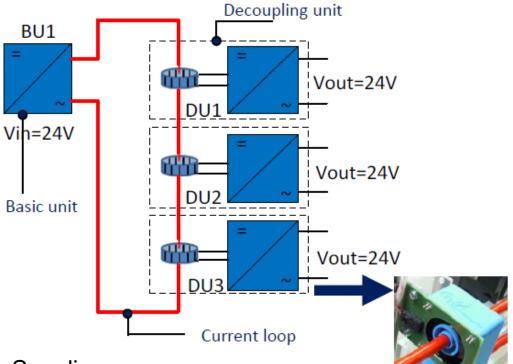

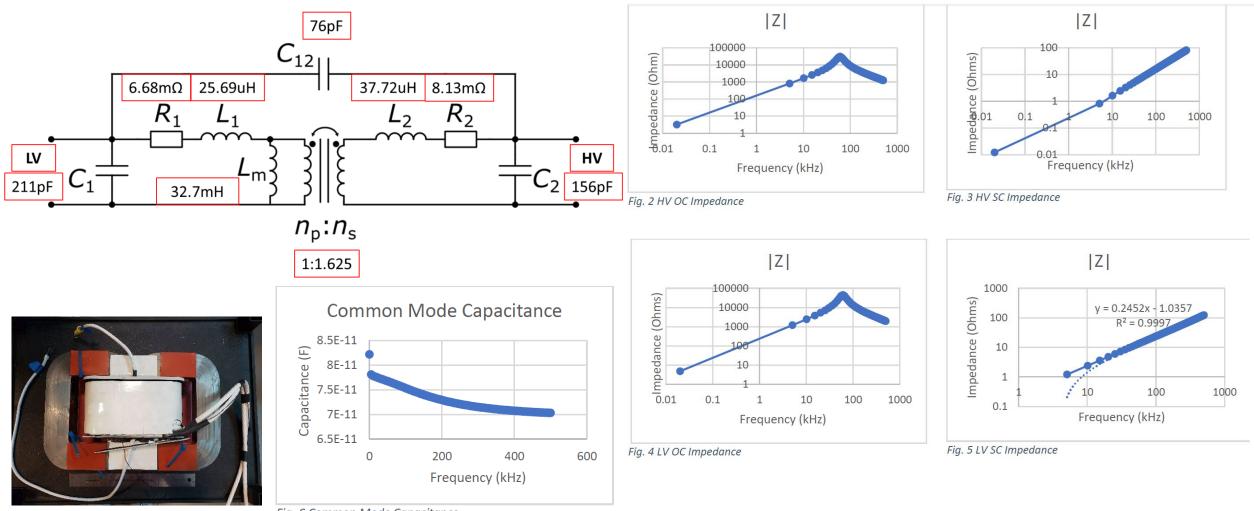

## MVSST Application: Fast EV Charging (Development)

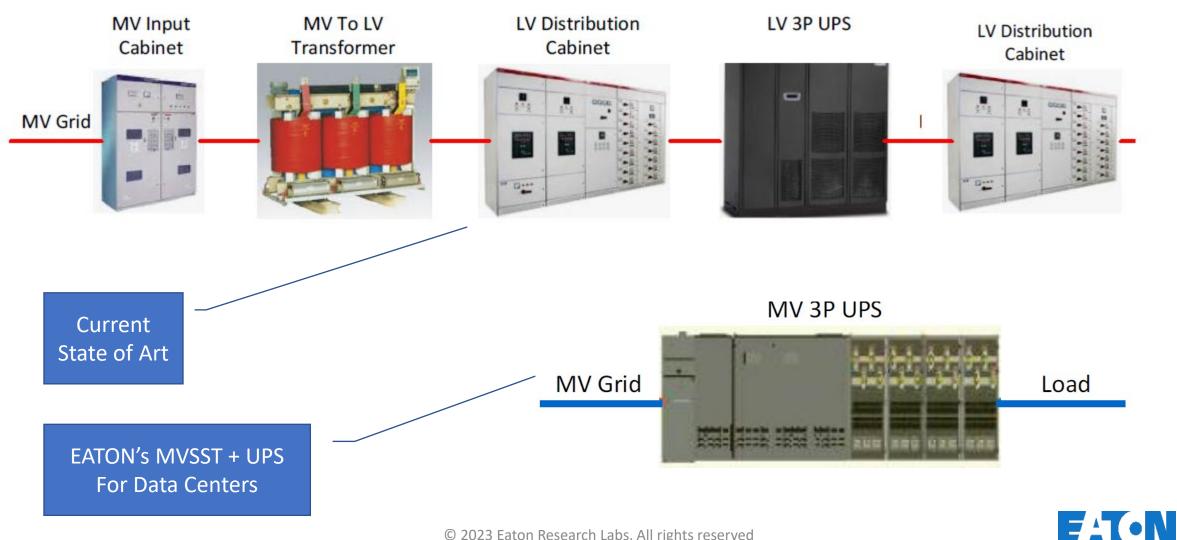

#### Data Center Power Distribution with MV SST

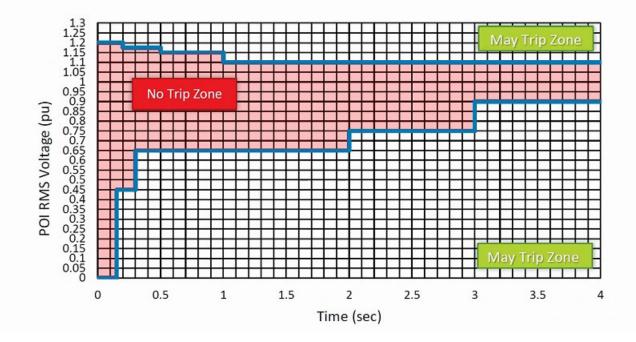

#### **Utility Connection Standards**

| High Voltage Ride-Through |                            | Low Voltage Ride-Through |            |

|---------------------------|----------------------------|--------------------------|------------|

| Voltage (p.u.)            | Time (sec)                 | Voltage (p.u.)           | Time (sec) |

| ≥ 1.2                     | Instantaneous Trip Allowed | < 0.45                   | 0.15       |

| ≥ 1.175                   | 0.20                       | < 0.65                   | 0.30       |

| ≥ 1.15                    | 0.50                       | < 0.75                   | 2.00       |

| ≥ 1.1                     | 1.00                       | < 0.90                   | 3.00       |

- IEEE 1547-2018 if exporting power

- CA Rule 21

- IEEE P2030.13

- SAE 1372

- IEEE 519-2022

- IEEE Std 1668<sup>™</sup>-2017

- ANSI C84.1-2020

#### Voltage Ride-Through Envelope

#### Critical Areas For SST Development

- Modular / Expandable Single Grid-Connecting Topology

- "Stackable" in Voltage

- Ease of paralleling

- Multi-functional (High Bandwidth)

- Grid-side control (power flow, voltage regulation, active filtering, supporting symmetry, active damping of transients)

- DC bus connected energy resources management

- Grid stability support

- Real-time energy dispatching

- Central Controller as dispatching and monitoring

- Smart Local Controllers handle modules operation and protection

- Use of Internal PLL for HF signal synchronization

- Self powering of individual levels (power Bootstrapping),

- Development of new core materials for high efficiency, high flux density HF Transformers

- XFR Flux "Centering" active controls  $\rightarrow$  further reduction of core volume

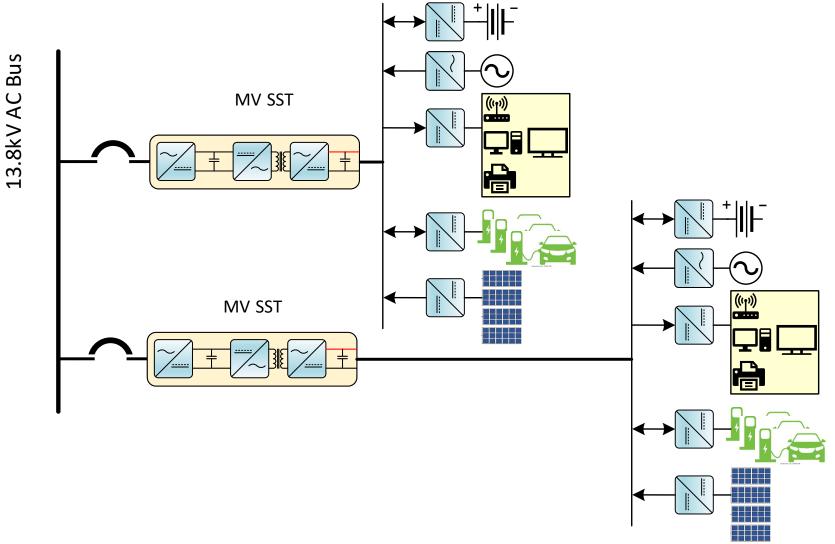

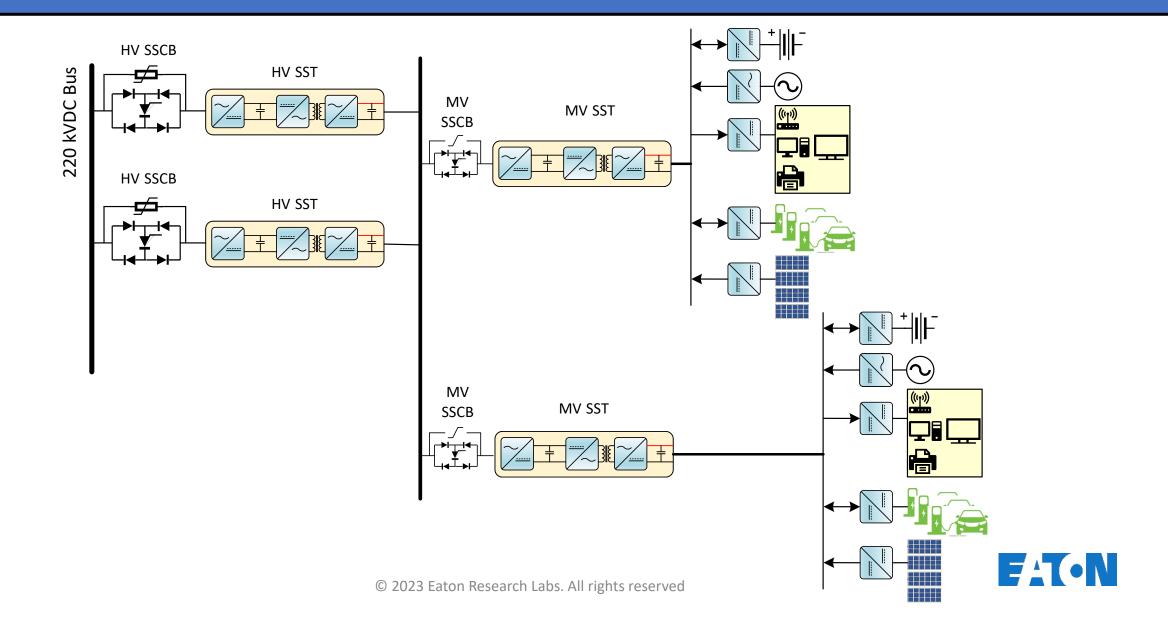

#### Transition to DC Transmission with MV SST

EAT ON

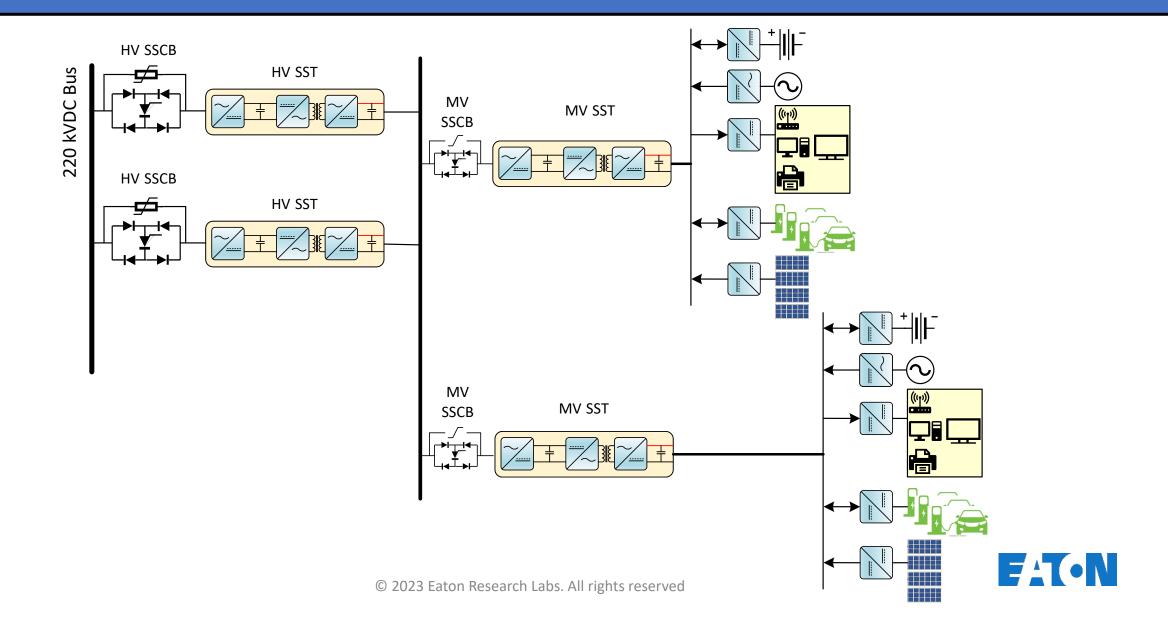

#### Transition to DC Transmission with HV SST

#### Transition to DC Transmission with HV SST

#### Thank You !

**Questions?**

Bogdan Borowy

Email: BogdanSBorowy@eaton.com